ARMando el Rompecabezas

Categoría: microcontroladores

Disertante: Ing. Sergio Caprile

Publicado: 30/09/2024 8:15 pm

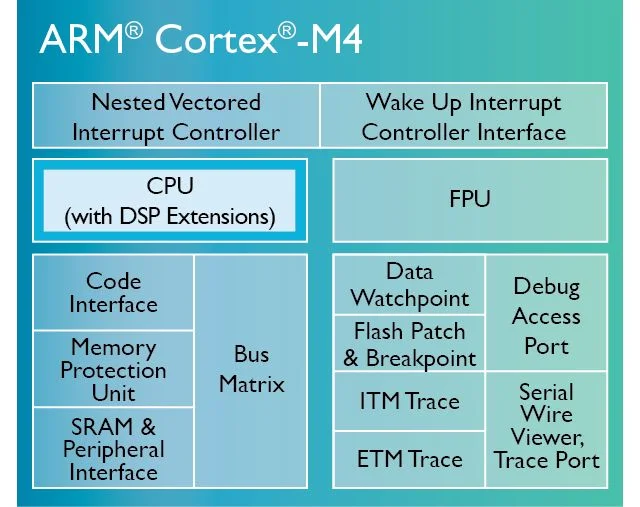

En el webinar se desglosa la arquitectura de los procesadores ARM, aclarando que ARM no fabrica procesadores directamente. En su lugar, ARM diseña y vende la propiedad intelectual (IP) de los cores de los microcontroladores. Fabricantes como ST o NXP integran estos cores con sus propios periféricos y buses para crear el producto final, lo que explica por qué muchos componentes son similares entre distintas marcas.

La desarrollan tres pilares fundamentales: la arquitectura, que define el set de instrucciones (los comandos que ejecuta el micro); el procesador, que implementa la arquitectura y su arquitectura de buses (se detallan las arquitecturas Von Neumann y Harvard, esta última con buses separados para instrucciones y datos); y la pipeline, la “tubería” donde las instrucciones se procesan en etapas (fetch, decode, execute), influyendo en la eficiencia.

Se repasa la evolución de ARM, desde sus inicios en los años 80 hasta las arquitecturas ARMv7 y ARMv8 (que introduce los 64 bits). Un punto clave es la característica de las instrucciones condicionales en el set de 32 bits de ARM. A través del ejemplo del algoritmo de Euclides, se demuestra cómo estas instrucciones (SUBGT, SUBLT) evitan los saltos (branches), optimizando la ejecución al no tener que “purgar” la pipeline.

Finalmente, se introduce el set de instrucciones Thumb (ARMv4) de 16 bits. Aunque reduce el rendimiento, su “genialidad” radica en el uso de un multiplexor que expande estas instrucciones a 32 bits, logrando mayor densidad de código y siendo una solución más económica en el contexto de memoria limitada de la época.

Todas las categorías:

- ASIC (2)

- Capacitación/Educación (8)

- Comunicaciones (8)

- Diseño (4)

- Edge Computing (1)

- fpga (2)

- Honorarios (1)

- Internet (3)

- microcontroladores (15)

- Modulación (2)

- open hardware (1)

- Radio (1)

- RTOS (5)

- Sensores (2)

- Sin categoría (1)

- Sistemas Operativos (6)

- software embebido (5)

- Soldadura (4)

- SoPC (1)